スプリアス規格が厳しくなり、VHFで50Wを超える送信機では、スプリアス抑圧比が70dBを求められる場合も出てきました。

VFOも、それに応じたスプリアスの少ないものにする必要があります。

シングルコンバージョンの場合、高い周波数のVFOも必要となります。

DDSや、ワンチップのPLLを使って、VFO単独でそのようなスプリアス比を得る事は難しいと考えました。

そこで頭に浮かんだのが、LC式のVCOと組み合わせて10kHzステップで発振するPLLと、その基準発振器をVXOにしてその間を補完する、シングルループのPLLです。

これであれば、周波数変換も無く、各バンドに各々一つのPLLを適切に作れば、スプリアスを非常に少なくすることが可能と思われました。

とは言っても、そんなVFOを是非作りたいのはスプリアス規格の厳しい50MHzです。HFにも、全バンドに使えるものがあればVFBですが、当面はオンエアの頻度が高めの7MHz用だけ、併せて搭載する事にします。従って、まずは2バンド用のVFOとなります。

<考え方>

例えば、12MHzのジェネレーターを用いて7MHzに出る場合、アッパー局発であれば19MHzのVFOが必要となります。

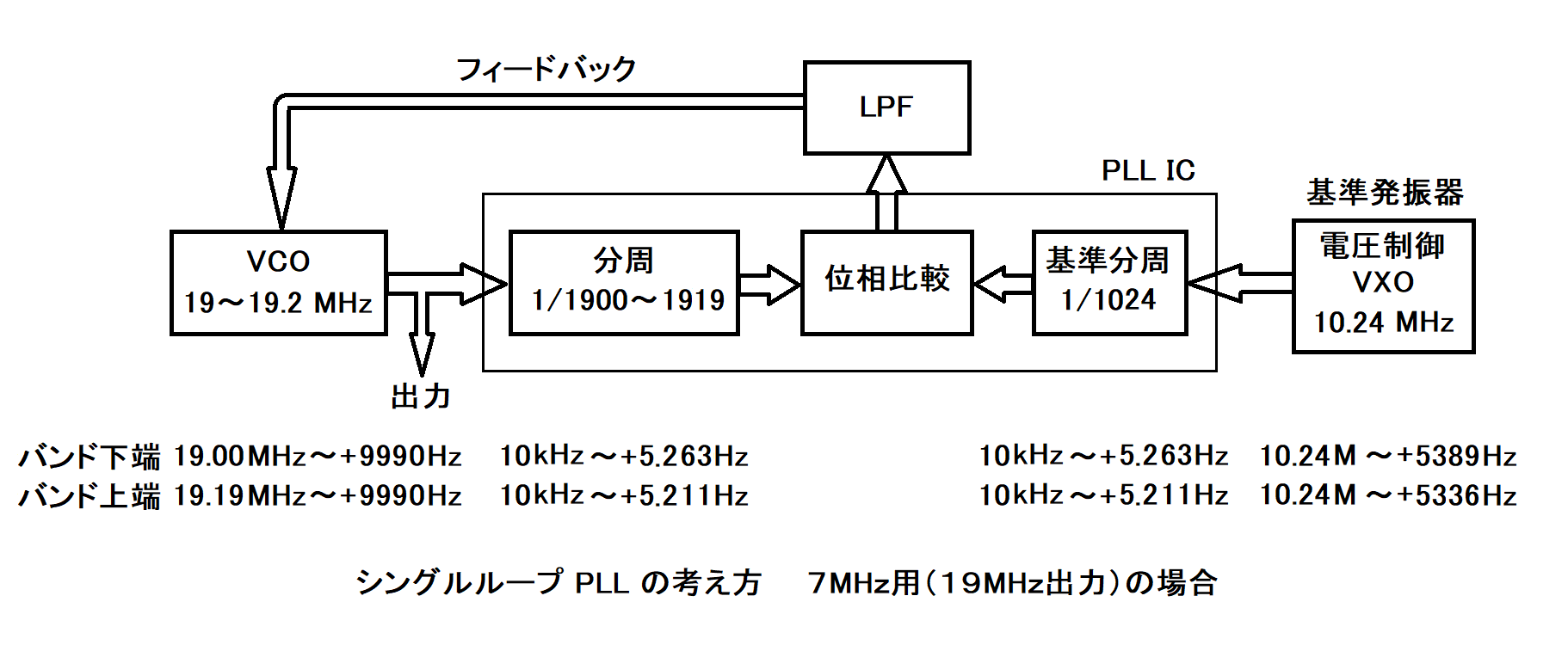

下の図は、その場合のシングルループPLLの考え方を示します。

19MHzから19.2MHz迄を、10KHzステップで発振させるPLLですが、右端の基準発振器がVXOになっています。

10kHz未満の端数を、このVXOで合わせます。バンドの下端から上端にかけて、分周比が1900から1919まで大きくなりますので、10kHz幅を生み出すためのVXOの発振周波数の幅は、バンド上端ではその分、少しだけ小さくなります。

VXOの可変範囲は5kHz程で、大きな範囲ではありませんが、これを電気信号で制御する必要があります。

しかしバンド全体で同じ周波数幅ではないため、分周比に応じた周波数幅を記録し、それに応じた制御電圧を作り出す必要があります。

1900~1919の分周比も電気信号で制御する必要があり、これらはマイコンで制御する事にします。

真ん中の位相比較器と二つの分周器は、一つのPLL ICでまかなう事にします。

その他のバンドについても、同じ考え方で構築します。

<基礎実験>

1.電圧制御VXO

電圧制御のVXOがうまく行かなければお話になりません。まずこれから実験しました。

10.24MHzから上へ数kHz可変できる水晶は、見つかりませんでした。

そこで、10.24MHzから下へ可変する事にしました。そのため、上図そのままは当てはまらなくなりました。^^;)

一つ上の分周ステップを用い、そこからVXOの周波数を下へ可変して、望みの基準周波数を得ます。

(これにより、各10kHzステップの基準周波数(可変範囲の下端になる)は、一定にならなくなりました。^^;)

バリコンはQが高く可変しやすいのですが、バリキャップでは可変範囲が少なくなりました。

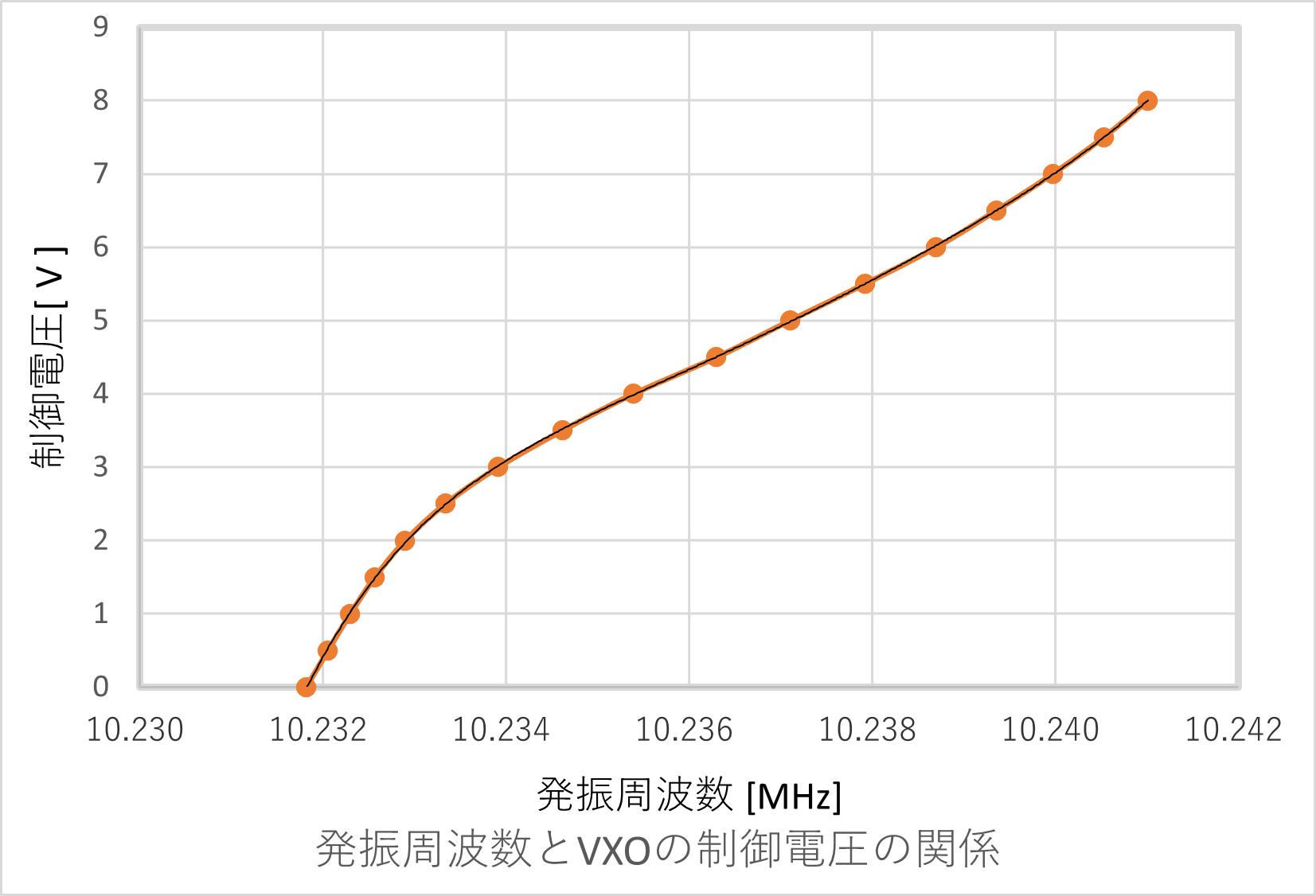

手持ちの10.24MHzの水晶を2個並列にし、バリキャップの電圧を2.5Vから7V程(7MHzの場合)まで変えて、目的の可変範囲を得ました。

その範囲の曲線を、直線になぞらえる事にします。

7メガより上のバンドでは、可変範囲はこれより少なくなります。

VXOの制御電圧対発振周波数の関係は、下の図の様でした。

2.DA変換器(DAC)とメモリー(EEPROM)

PLLの周波数は10kHzステップですが、その間を500で割り、20HzステップでVFOの出力周波数を可変する事にします。

これくらいにすれば、ダイヤルを回した時のステップ感が殆どありません。

そこで、バンドの下端から上端まで、10kHz毎に、出力すべき電圧をデジタルに変えて、予めメモリーに記録しておきます。

DACはMCP4821を用いますが、出力電圧は5V迄なので、これをオペアンプLM358を用いて2倍に増幅します。

ロータリーエンコーダーを用いてマイコンからDACにデータを入力し、出力電圧を実測する実験を予め行いました。

EEPROMメモリーには25LC640Aを用います。ここへ出力周波数の10KHz幅に対応するVXOの制御電圧に応じたDACデータ値と、その幅を500で割った値を、記録しておきます。データはExcelシートで用意し、やはりExcelを用いてhexファイルを生成、これをPICKit3でEEPROMに書き込んでおきました。

このデータをマイコンで読み出し、前記500で割った値と、10kHzステップからの出力周波数の偏移を20Hzで割った値を掛け合わせ、10kHz毎のデータに加算して、DACに送るデータとします。

3.PLL IC

装置の心臓は、このPLL ICです。

発振周波数は、7MHzの場合は19MHz、50MHz場合は62MHzと行きたいところですが、VXOのドリフトと、VXOの可変範囲が狭くなることからの誤差拡大を懸念し、50MHzだけはローワーの38MHzとしました。

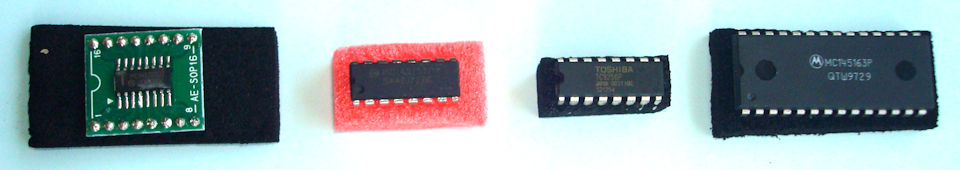

これらの範囲で安定に動作するPLL、またシリアル制御できるICとして、モトローラのMC145170を使いたかったのですが、純正品が入手できませんでした。ネットで隣国から購入したフラットパッケージの物は、ロックしませんでした。どうも、不良なまがい物だったようです。

入手できたのは、MC145157と、TC9256でした。

MC145157は、max15MHzとあります。それでも19MHzはうまく発振しました。しかし、38MHzはさすがに無理でした。

TC9256は、38MHzでもしっかりとロックしたのですが、分周比として1024を選ぶことが出来ないため、VXOからやり直しとなります。

手持ちにMC145163があったので、テストしてみました。これは期待に外れたことが無く、しっかりロックしたのですが、制御がパラレルのBCDのため、

制御の一部をBCDで構築しなければなりません。また大型で、シリアル-パラレルの変換も必要になります。う~ん。

BCD扱い等の面倒を我慢してMC145163か、VXOからやりかえてTC9256か。

結局、発振出力をゼネカバ受信のトランシーバーで比較し、トーンに不純な成分が何も感じられなかったMC145163を選びました。

シリアル→パラレルの変換には、74HC595を2個使います。

テストしたPLL IC 左から MC145170(まがい物?)、MC145157、TC9256、MC145163

4.制御用マイコン

制御の対象は、PLL、EEPROMメモリー、DACとあり、これらとはSPIでの通信が必要です。ディスプレイにもコマンドを送る必要があります。

さらに、入力にはロータリーエンコーダー、スイッチ類その他あります。

実験の初めは、18ピンのPIC16F819でダイナミックLEDディスプレイを使い、DACやEEPROM、PLLそれぞれと単独に通信してテストしていましたが、全体を考えると、28ピンが2個か、40ピンのマイコンが必要です。

IOの数、また割込み可能なIOを多くとれる事と、少しずつ構築してテスト出来る事から、28ピンの16F1786を2個使う事にしました。

<VFOの基本構成>

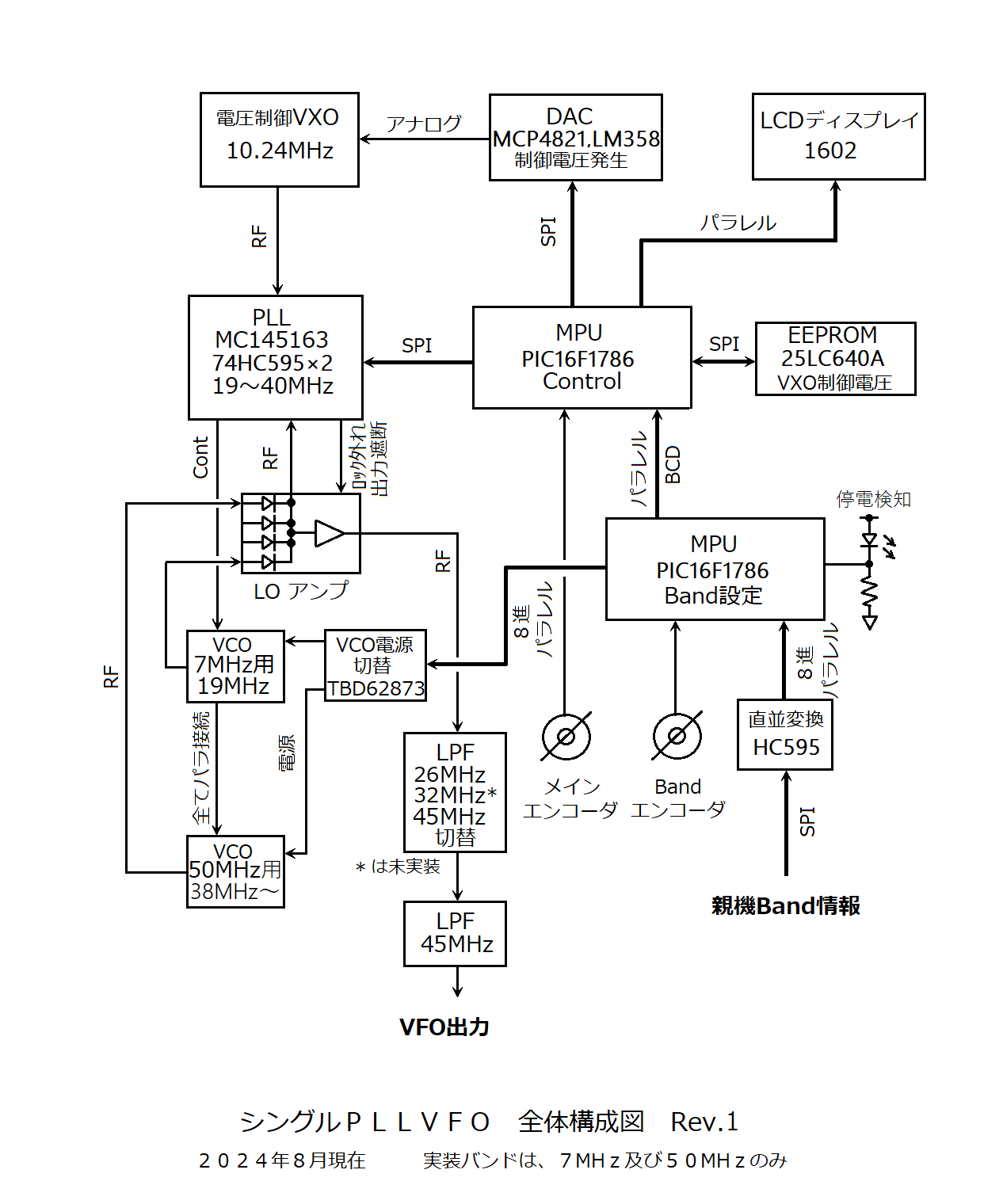

以上を反映し、VFOの全体構成は下図のようになりました。

全体を制御するマイコン、PIC16F1786(control)が中心になります。これが、PLL、DAC、EEPROMにSPIでアクセスし、コントロールします。

これらの連携については、前述のとおりです。

LCDディスプレイはパラレルでコントロールしています。また、選局用のメインエンコーダの信号、RITやメモリー等のスイッチ信号を受け入れます。

また、別途のメモリーには、装置が停止する寸前に、現在の設定周波数を記録し、起動時に再現するようにしました。

親機のトランシーバーにはバンド切替情報の出力(SPI)があるので、それによる切替えとともに、単独運転用にエンコーダによる切替も出来るようにします。

初め、ロジックICの組み合わせにしようかと思いましたが、それよりマイコンを使えば回路が簡素化し(ソフトが作成必要ですが。^^;)、また割込みも使用できることから、ちょっともったいないですが同じマイコン、16F1786を使う事にしました。

このマイコンが、バンド用エンコーダの他、74HC595を用いて親機のBAND情報を受け入れ、処理してメインのマイコンに送ります。また、一部のプッシュスイッチ信号を、ワンショットに整形する内職もします。hi.

それから、電源電圧の低下を検出し、メインのマイコンに停止寸前の周波数記録のための割込み信号を出します。

VCOは複数を使う事になります。一方の出力が他のVCOに繋がって損失が生ずるのはマズいので、LOアンプ(AD8045使用)の中のダイオードスイッチで、使用中のVCOに切り替えます。また、万一のロック外れの時は、このアンプの電源を停止し、リレーでVCO出力を地絡します。

<制御ソフトについて>

選局に関わる周波数のアップダウンカウンター、中間周波数の加減算、周波数メモリーといった、周波数の主要な取り扱いは、BCDとしました。

バイナリで扱う場合、表示やPLLのためにBCDへ変換が必要ですが、この変換の方が、BCDからEEPROMやDACで必要なバイナリに変換するより、コスト高のようなので、決めました。

周波数として扱うのは、10Hz台から10MHz台までの7桁ですが、BCDで4バイトとなり、Hzの桁も”0”として一応計算対象となります。

下の図は、エンコーダーで入力した4バイトBCDのアップダウンカウンターの数値から、PLLとVXOを動かすまでの処理の流れを示します。

(実際の数値には端数もあり、A/B VFOやメモリーの処理、バンド切替えなどもあります。)

出力周波数は、上位2バイトと下位2バイトで処理が別フローになるところがミソです。hi.

<製 作>

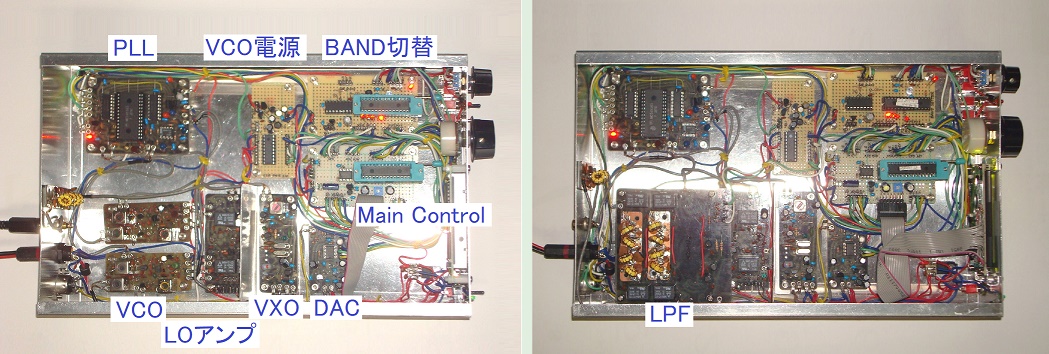

装置は、シャーシをひっくり返し、コの字型のカバーをかけたケースの中に組み立てました。

製作途中と、その後の内部の様子が、下の写真です。

写真左 製作途中 写真右 その後

右の写真には、二つのVCOの上部に取り付けられたLPFが写っています。

VCO電源は、バンド毎に切替えてVCOに電源を送るものです。また、ロック外れの時はLOアンプの電源を落とします。

メイン コントロールユニットのマイコンには、トライアルやバージョンアップのため、ゼロプレッシャソケットを使っています。BAND切替えのマイコンのものは、もう外しました。hi.

この装置、アイデアは以前から温めていたものでした。

しかし時間が余りとれない時期もあり、実験を始めてから2バンドで使えるようになるまで、2年ほどかかりました。^^;)

<微弱な回り込み>

スプリアスも、-70dBやさらに下回るレベルを狙っていると、思わぬ所から来る、別の信号の回り込みが見つかるようになります。

下記の回り込みには、対策が必要でした。

① PLLユニットからVCO出力ラインへの、基準発振信号(10.24MHz)の逆流

まさかと思いました。スペアナで当たると、VCOのバッファーアンプまで逆流が及んでいました。

PLLユニット内にパスコンや、アースパターンの連結(ジャンパー線)を増設しました。しかしそれでも不十分でした。

VCOにPLL行き用のバッファーアンプと、出力ラインのバッファーアンプの二つを設けて、ようやく逆流を退治しました。

② VXOからLOアンプへの基準発振信号(10.24MHz)の直接の飛び込み

これら二つの間にシールド板を立てると、飛び込みが無くなりました。(先に、仮のアルミ板を手持ちで挿入して、効果を確かめました。)

③ 出力遮断中にかすかな出力漏れ

親機の内部VFO(DDS)を使用中(リレーで切替え)は、当装置内のLOアンプへの電源を遮断し、入力側と出力側をリレーで地絡していました。それでも受信中にPLLのダイヤルを回すと、かすかに信号が聞こえました。大変意外でした。

そのため、親機内部のVFO使用時は、VCOへの電源も遮断するように改造し、出力漏れを無くしました。

<スプリアスの低減状況は・・・>

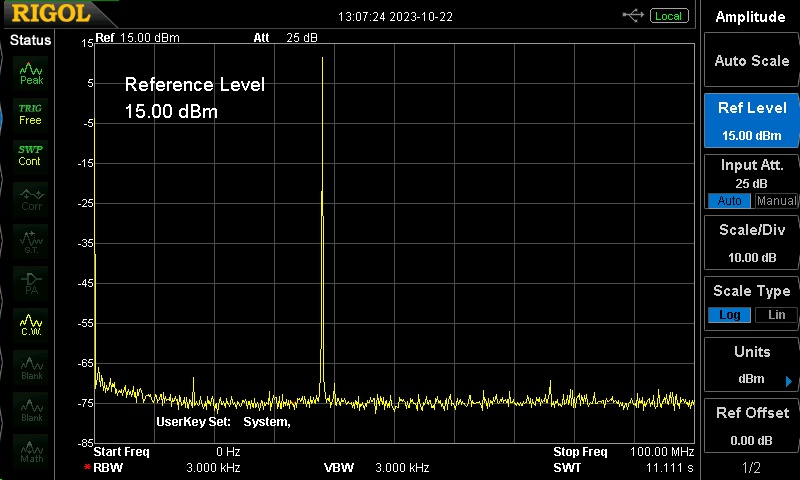

スプリアスは、7MHz用は余裕をもって規格をクリアし、気になる50MHz用(38MHz出力)でも、下図のように-80dBに達しています。

(スケールが+15dBmから-85dBmと、少し見づらいですが。^^;)

<試してみて>

使い心地はDDSの場合と何も変わりません。

周波数の変化ステップは20Hzなので、選局はスムーズです。ただ、たまに周波数の変化が大き目のステップがあります。PLLのステップ切り替わりにVXOが完全には合せ切れていないと思います。しかし逆行する程のものではありません。

また、この切り替わりの時に、PLLが瞬時ロック外れをするだろうと思っていましたが、全く判らない程度でした。

ダイヤル1回転あたり約8kHz動くので、ワッチは楽です。演算が多いためか、早回しすると8kHzが6kHzなどに減ります。無茶な回し方はできません。hi. 急ぐ時は、ステップを100Hzに切り替えます。

VXOの周波数対制御電圧の関係は曲線ですが、これを直線になぞらえています。周波数には多少の誤差が含まれると思いますが、気になるほどではありません。(鈍感力がついてきた?)

A/B VFOや、周波数メモリー、停止した時の周波数で次に立ち上がるメモリーは、便利です。

この装置は、棚と他の装置の隙間に入るよう、扁平に作ったのですが、横向きには入らず、縦置きになってしまいました。

首を少しかしげてディスプレイを見ています。

私は右利きなので、ダイヤルツマミをディスプレイの右側に取り付けたのですが、縦になったため上側になり、ディスプレイを見るのに手が少し邪魔です。そこまでは考えが及んでおりませんでした。hi.

長くなりました。最後までお読みいただき、ありがとうございます。