VFOやトランシーバーの製作にも、今やロータリーエンコーダーは普通になっているのではないでしょうか。

周波数増減のステップは細かくしたいし、そうするとダイヤルツマミをくるくる回しても、なかなか周波数が変わっていかない、ワッチが面倒くさい、となりがちです。

ステップを100Hz位にすると、周波数の増減は楽ですが、復調トーンはドレミファくらいに階段状に変化して、ゼロインしにくい・・・。

エンコーダーの読み取り処理(デコード)が4倍精度(公称パルス数の4倍の速度が得られる)になっていればFBですが、目前の装置は単精度。

こういう時、エンコーダーと読み取り回路(デコーダー)の間に入れて、4倍精度で読み取り、単精度のデコーダーを4倍速で働かせる、いわばエンコーダー増速器を作れないかと考えました。

<4倍精度デコードの仕組み>

ロータリーエンコーダーの出力は、下図のように90度位相で2信号あります。

上段の方形波で示すφ0の信号を、左から右へとたどる時、信号が矢印の様に立ち上がる時にφ1がHighであれば、エンコーダーが右回転したと解釈し、パルスを1つ出します。

これをさらに続けると、黒星の所で次々にパルスが出ます。これが単精度のデコードです。

これに対し、φ0、φ1のどちらかでも変化した時にパルスを出すなら、白星の所でもパルスが出ます。都合、4倍のパルスが得られます。これが、4倍精度のデコードです。

図のφ0の方形波を、右端から左にたどれば、今度は信号の立ち上がりでφ1はLowになります。これで、左回転したものとして、先程同様にパルスを出す事ができます。

<単精度デコーダー用信号の吐き出し>

吐き出しというと、何だかコンパイラーみたいですね。

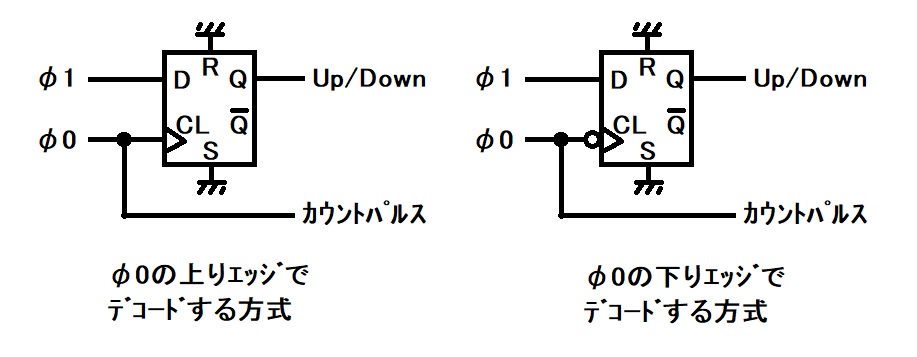

単精度デコーダーの種類は色々あるのかもしれません。よく目にするのは、下図左のようなものです。

勿論、右のものもあります。

左の図は、φ0がHighになる瞬間のφ1の値のHigh/Lowを、Up/Downの識別として出力し、またφ0をそのままカウンターへのクロックパルスとして出力するものです。

これをそのままマイコンで実現するものもあります。

右の図は、φ0がLowになる瞬間に、同様に処理するものです。

それであれば、先の説明のように、4倍精度でデコードしたパルスが来るたびに、下のような信号を吐き出せばよいと考えました。

パルスはかなり短いものです。エンコーダーの動きに追いつかれないためです。hi.

上りエッジ用の出力は、φ0がLow、φ1がHighというのが平常のレベルになります。

下り用であれば、両方Highが平常状態です。

これが、本物のエンコーダーとの違いです。hi.

しかしこれでも、先の回路図のデコーダー、或はそれと同じ機能を持つマイコン等のデコーダーで処理できると考えられます。

その他の原理で働くデコーダーで処理できるかどうか判らないのがちょっとつらいところ、表題を”試作”と称している所以です。^^;)

<この増速器が使えない場合>

クリック付きのエンコーダーは、先の「4倍精度デコードの仕組み」の図にある☆の所を実質的にスキップしてしまうので、この増速器が使えません。

装置側のデコードの方法が、前記のデコード方法と異なる場合も、動作しない可能性があります。どうもすみません。

またこの増速器は、単精度のデコーダーの前に取りつけるものです。既に4倍精度のデコーダーをご使用の場合には使えません。

<製 作>

以上のような機能を、PICマイコンで実現します。回路図は次のようなシンプルな物です。

ジャンパーが二つあり、クロックの上りエッジ用/下りエッジ用の選択のほか、2倍精度/4倍精度も選べるようにしました。

LEDは、開発段階での動作確認のために付けていましたが、動作時に光ると楽しいので、付けたままにしています。

製作には、蛇の目基板を使いました。下の写真のように、とても小さく作れます。

以前ワイヤロジックで製作した4倍精度デコーダーのサイズと比べると、夢のようです。

この増速器は、JK1XKP貝原さんのKP6D(リンクはこちら)というキットを応用したHFトランシーバー(リンクはこちら)に取り付けようと思ったのが製作のきっかけでした。

マイコンは当初、エンコーダーを操作しない時も作動するようプログラミングしたのですが、その後、使っていない時に停止(スリープ)するように変えました。スリープのプログラミングに当たっては、貝原OMのアドバイスをもらいました。

<使ってみる>

前記トランシーバーは前記のD-FFの下りエッジでの動作を実現するプログラムをマイコンに搭載しています。この増速器の動作試験に使い、正常動作を確認したので、増速器はそのまま組み込みとなりました。

また、80年代に製作したPLL VFOでは、RITエンコーダーの信号を、D-FF(上りエッジ動作)でデコードしていたので、これにも取り付けました。φ0とφ1の区別を確認していなかったので、次のような状況になりました。

・エンコーダーを左に回すと、周波数が上がっていく

・エンコーダーを右に回すと、周波数が変化しない

そこで、出力側接続のφ0とφ1を入れ替えると、正常に動作するようになりました。

組み込み後の状況は、下の写真のようです。シャーシの端の小さな隙間に取り付けました。

エンコーダーを操作中なので、LEDが光っています。よく見ると、φ0とφ1の配線を取り換えたのが判ります。

<動作がおかしい場合は・・・>

自作機で、φ0とφ1が識別されていないケースは、多いと思います。

動作がおかしい場合は、次の方法を試すと良いと思います。

・ エンコーダーを右に回すと、周波数が下がり、左に回すと周波数が上る。

→ エンコーダー接続の、φ0とφ1を入れ替える。

・ どちらか一方に回すと周波数が変化するが、逆に回すと不作動、ないし誤作動

→ 出力側接続のφ0とφ1を入れ替える。

・ どちらも誤作動、ないし不作動

→ デコーダーが上りエッジ動作か、下りエッジ動作かを再確認する。

確認結果に合わせて、J2を修正する。

現在のデコーダーが、エンコーダーの処理にかなり時間をかけている場合は、パルス幅を現状の500μSより長めに変更する必要があります。

<トライしてみよう>

トライしてみようとお考えの場合、ソフトの提供などのご相談をお受けします。

トップページの下欄から、E-mailをお送りください。

前のページへ

Home Page